聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

Xilinx

+關(guān)注

關(guān)注

73文章

2205瀏覽量

131802 -

Vivado

+關(guān)注

關(guān)注

19文章

860瀏覽量

71371

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

Vivado中IP核被鎖定的解決辦法

當(dāng)使用不同版本的Vivado打開(kāi)工程時(shí),IP核被鎖定的情況較為常見(jiàn)。不同版本的Vivado對(duì)IP核的支持程度和處理方式有所不同。

Vivado時(shí)序約束中invert參數(shù)的作用和應(yīng)用場(chǎng)景

在Vivado的時(shí)序約束中,-invert是用于控制信號(hào)極性的特殊參數(shù),應(yīng)用于時(shí)鐘約束(Clock Constraints)和延遲約束(Delay Constraints)中,用于指定信號(hào)的有效邊沿或邏輯極性。

通過(guò)vivado HLS設(shè)計(jì)一個(gè)FIR低通濾波器

Vivado HLS是一款強(qiáng)大的高層次綜合工具,可將C/C++代碼轉(zhuǎn)換為硬件描述語(yǔ)言(HDL),顯著提升FPGA開(kāi)發(fā)效率。

AMD Vivado Design Suite 2025.2版本現(xiàn)已發(fā)布

AMD Vivado Design Suite 2025.2 版本現(xiàn)已發(fā)布,新增對(duì) AMD Versal 自適應(yīng) SoC 的設(shè)計(jì)支持,包含新器件支持、QoR 功能及易用性增強(qiáng)。

vivado時(shí)序分析相關(guān)經(jīng)驗(yàn)

vivado綜合后時(shí)序?yàn)槔饕怯袃煞N原因?qū)е拢?1,太多的邏輯級(jí)

2,太高的扇出

分析時(shí)序違例的具體位置以及原因可以使用一些tcl命令方便快速得到路徑信息

發(fā)表于 10-30 06:58

vcs和vivado聯(lián)合仿真

我們?cè)谧鰠①愓n題的過(guò)程中發(fā)現(xiàn),上FPGA開(kāi)發(fā)板跑系統(tǒng)時(shí),有時(shí)需要添加vivado的ip核。但是vivado仿真比較慢,vcs也不能直接對(duì)添加了vivado ip核的soc系統(tǒng)進(jìn)行仿真。在這種情況下

發(fā)表于 10-24 07:28

FPGA開(kāi)發(fā)板vivado綜合、下載程序問(wèn)題匯總

在做vivado綜合時(shí)和FPGA下載程序時(shí),我們碰到以下問(wèn)題,并找出了對(duì)應(yīng)的解決方案。

1.could not open include file”e203_defines.v”問(wèn)題

在做

發(fā)表于 10-24 07:12

Vivado中向FPGA的Flash燒錄e203的方法

首先導(dǎo)入、并配置好項(xiàng)目,完成項(xiàng)目的綜合(SYNTHESIS)與實(shí)現(xiàn)(IMPLEMENTATION),查看有無(wú)錯(cuò)誤與或警告信息,調(diào)整完成后,右鍵比特流生成(Generate Bitstream),選擇

發(fā)表于 10-23 08:28

【RA4M2-SENSOR】+手機(jī)控制RGB_LED彩燈變換

)

{

R_IOPORT_PinWrite(&g_ioport_ctrl, BSP_IO_PORT_00_PIN_02, BSP_IO_LEVEL_HIGH);

R_IOPORT_PinWrite

發(fā)表于 09-19 20:02

vivado仿真時(shí)GSR信號(hào)的影響

利用vivado進(jìn)行設(shè)計(jì)xilinx FPGA時(shí),寫(xiě)完設(shè)計(jì)代碼和仿真代碼后,點(diǎn)擊run simulation(啟動(dòng)modelsim進(jìn)行仿真)。

Vivado無(wú)法選中開(kāi)發(fā)板的常見(jiàn)原因及解決方法

在使用 AMD Vivado Design Suite 對(duì)開(kāi)發(fā)板(Evaluation Board)進(jìn)行 FPGA 開(kāi)發(fā)時(shí),我們通常希望在創(chuàng)建工程時(shí)直接選擇開(kāi)發(fā)板,這樣 Vivado 能夠自動(dòng)配置

如何使用One Spin檢查AMD Vivado Design Suite Synth的結(jié)果

本文講述了如何使用 One Spin 檢查 AMD Vivado Design Suite Synth 的結(jié)果(以 Vivado 2024.2 為例)。

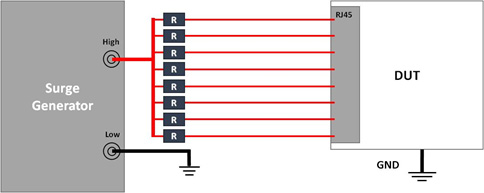

“System Level EOS Testing Method”可以翻譯為: “系統(tǒng)級(jí)電性過(guò)應(yīng)力測(cè)試方法”

“System Level EOS Testing Method”可以翻譯為:

“系統(tǒng)級(jí)電性過(guò)應(yīng)力測(cè)試方法”

Vivado 2018.3軟件的使用教程

大家好,歡迎來(lái)到至芯科技FPGA煉獄營(yíng)地,準(zhǔn)備開(kāi)啟我們的偉大征程!正所謂“兵馬未動(dòng),糧草先行”,戰(zhàn)前的準(zhǔn)備自是必不可少,在FPGA的漫漫沙場(chǎng),我們何以入場(chǎng),何以取勝呢?在這里我們?yōu)楦魑粦?zhàn)友準(zhǔn)備了vivado 2018.3的使用教程。

Getting Started with Vivado High-Level Synthesis

Getting Started with Vivado High-Level Synthesis

評(píng)論